Verilog Syntax

Remembering syntax for any coding language is very vital for writing good codes. So let's look into the different Verilog syntax.

Module

module keyword is used to declare a module which is the basic building block of verilog code. A module always have a associated endmodule keyword, which marks end of the module.

Comments

Comments are important part for professional coding as it increases readability of the code. In Verilog, there are 2 types of comment.

-

Single-line comment —

//is used to write single line comment. -

Multi-line comment — This is used to write comments which extends to more than 1 line. Multi line comments start with

/*and ends with*/. Everything between these 2 keywords is treated as comment.

Operators

Operands

The variable upon which the operation is done is known as operand.

Different Operators

Operators are used to create expressions. Operators are basically of 3 types depending upon the number of operands it has.

- Unary Operator — It has only one operand. Ex -

x = ~a - Binary Operator — It has 2 operands. Ex -

x = a + b - Ternary Operator — It has 3 operands. It acts as a replacement of if-else. Ex -

x = a ? b : c. This means that ifais true, i.e., 1 thenxwill be assigned value ofb, otherwise value ofcwill be assigned tox.

Number Literals

As Verilog represents a hardware and in hardware different base numbers are used, thus Verilog supports different type of number systems base. Also, the way of writing a number literal is different in Verilog. Also, hardware can work even on single bit data or even on 32- or 64-bit data, thus for every number literal we need to provide the number of bits.

This is the syntax to write a number literal in Verilog.

[no_of_bits]’[base][numerical_value]

Where,

no_of_bits = size of the literal

base = base of the number, it can take these values b or B for binary, o or O for octal, d or D for decimal, and h or H for hexadecimal

numerical_value = value of the number in the specified base

Example

String Literals

Any literal between " " is treated as string by Verilog. Strings can be thought of as array of characters. Verilog uses ASCII to store the characters and thus each character requires 8-bit or 1-byte.

String literals cannot be written in multiple lines.

Example

Identifiers

Identifiers are any text which is used as a variable name. These text or strings are used to identify a particular variable, module, etc.

In Verilog there are some rules which needs to be followed for identifiers:

- Identifiers can only contain

[0-9][A-Z][a-z]and_or$. - Identifier should not start with

$or[0-9] - Identifier should not contain only numbers.

- Identifier should not contain any white spaces.

- Identifiers are case sensitive. That means

half_adderandHalf_adderare 2 different identifiers. - Keywords cannot be used as identifiers.

Example

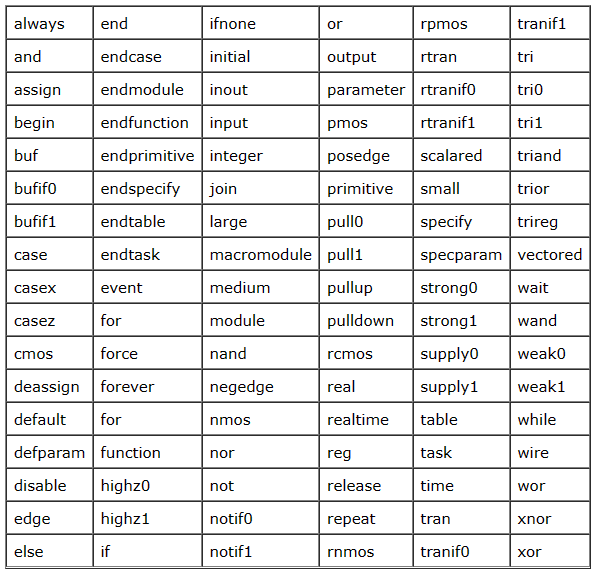

Keywords

Keywords are special literals which has certain meaning to Verilog language. These keywords should not be used as identifiers, as Verilog will interpret it as keywords.

Some of the keywords are:

We will know more about the keywords as we move forward.

Try different syntax in Eda Playgorund